6月30日上午消息,近日台积电(简称tsmc)正式在中国上海召开年度技能论坛,发布了其最新的技能路线,以及备受重视的2纳米制程相关技能进展。

在曩昔的两年里,新冠疫情肆虐,但在另一面,这场疫情加快了数字化转型,影响渗透至各个工业。科技的前进大幅地协助和改变了企业及人们的工作方式,不再遭到距离的限制。

也正是因此, 全球半导体工业的营收大幅增加,根据第三方组织Gartner的数据,半导体工业营收增长率超越25%。该趋势估计将在这十年的剩下时间内持续下去,2030年曾经估计到达年营收1兆美元。

总结现有技能,台积公司采用 N7 和 N6 技能的客户产品组合不断扩大,从智能手机、CPU、GPU 和 XPU,延伸至射频和消费电子使用。根据官方数据,2022 年底曾经,产品规划定案的累积数量将超越400。

台积公司的 5 纳米技能现已进入量产的第三年,支持智能手机、5G、AI、网络和 高功能核算工业的产品使用。台积电在持续提高 N5 和 N4 技能,估计到本年年底将有超越 150 个产品规划定案。而且现已将 N4、N4P 和 N4X 技能加入咱们的 5 纳米宗族,为即将到来的 5 纳米产 品供给持续的 PPA 晋级。 别的,台积电发布,从 N5 到 N4X,功能提高了 15%,芯片密度提高了 6%,一起坚持规划规则的兼容性。

去年台积电宣告了的N5A,针对轿车工业使用的晋级。现在,N5A规划生态系统估计在本年第三季获得轿车等级认证。

台积公司 3 纳米工艺技能持续采用 FinFET 半导体结构。他们认为此工艺的功能和技能成熟度将最能够满足工业的需求。N3工艺按计划于2022年下半年量产。N3E将于 2023 年下半年量产。

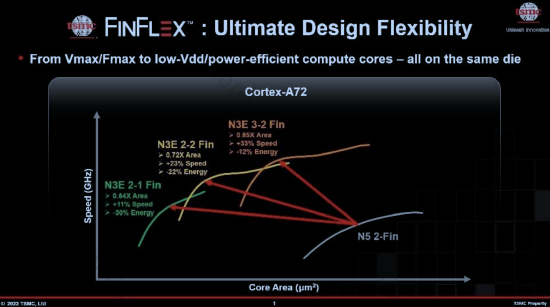

本年,台积电在 3 纳米技能上推出了 TSMC FINFLEXTM 架构,它结合了工艺制程和规划的创新,并供给良好规划弹性,从而优化高功能、低功耗到达两者的平衡。

关于2纳米宗族,台积电提到,在曩昔的 15 年中,他们一直在研究纳米片(nanosheet)晶体管,相信 N2 是导入纳米片晶体管的合适工艺制程,将速度和功率提高全一 代,协助客户坚持竞争力。N2 的开发按计划顺利推动,估计于 2025 年量产。 在纳米片晶体管和规划技能协同优化(DTCO)的协助下,台积公司 N2 的功能和 功率优势提高了一代。相较于 N3E,在相同功耗下速度提高 10-15%,或在相同速 度下功耗降低 25-30%。

因为纳米片晶体管具有卓越的低 Vdd 功能,N2 在正常 Vdd 及相同的功耗下,功能提高了 15%,在较低的 Vdd(0.55V)下,优势扩大到 26%。

多年来,规范半导体架构的演变现已从平面式晶体管转至鳍式场效晶体管 (FinFET),并将再次发展到纳米片晶体管。在纳米片之外,台积电看到未来有许多可能的方向,包含 CFET(笔直堆栈的 nFET 和 pFET)。 而且还期待在2D资料、1D碳纳米管等方面的打破,在不断微缩的一起,战胜芯片移动性方面的应战。 未来,台积公司将持续探究晶体管架构,并使用2D资料和碳纳米管等新资料。